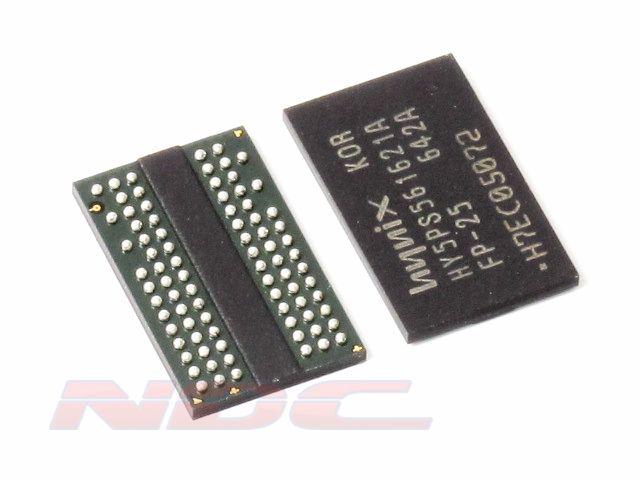

Hynix HY5PS561621A 256Mbit DDR2 BGA SDRAM

For shipments outside the UK, we offer both Excl. VAT & Duties Prepaid options during checkout, if a prepaid option is not selected tax/duties may be payable upon import in your country.

Hynix HY5PS561621A • VDD ,VDDQ =1.8 +/- 0.1V • All inputs and outputs are compatible with SSTL_18 interface • Fully differential clock inputs (CK, /CK) operation • Double data rate interface • Source synchronous-data transaction aligned to bidirectional data strobe (DQS, DQS) • Differential Data Strobe (DQS, DQS) • Data outputs on DQS, DQS edges when read (edged DQ) • Data inputs on DQS centres when write(centred DQ) • On chip DLL align DQ, DQS and DQS transition with CK transition • DM mask write data-in at the both rising and falling edges of the data strobe • All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock • Programmable CAS latency 3, 4, 5 and 6 supported • Programmable additive latency 0, 1, 2, 3, 4 and 5 supported • Programmable burst length 4 / 8 with both nibble sequential and interleave mode• Internal four bank operations with single pulsed RAS• Auto refresh and self refresh supported • tRAS lockout supported • 8K refresh cycles /64ms • JEDEC standard 84ball FBGA(x16) • Full strength driver option controlled by EMRS• On Die Termination supported • Off Chip Driver Impedance Adjustment supported • Self-Refresh High Temperature Entry • Partial Array Self Refresh support.

| Manufacturer Part # | HY5PS561621A |

|---|---|

| Manufacturer | Hynix |

| Item Condition | New |